PowerPC

PowerPC (PPC) ist eine Mikroprozessor-Architektur, die 1991 durch ein US-amerikanisches Konsortium der Unternehmen Apple, IBM und Motorola (ab 2004 Freescale) – auch kurz AIM genannt – spezifiziert wurde. Im Jahr 2005, markiert durch den Rückzug mehrerer führender Teilnehmer und durch die Aufgabe des klassischen PC-Bereichs als Anwendungsziel, sank die Relevanz der Plattform für den öffentlich sichtbaren Bereich erheblich. Ab 2006 wurde unter dem Namen Power.org die Kern-Serie 2 weiter gepflegt. Im Jahr 2017 steht eine gepflegte Version 3 des Kerns mit dem Attribut "OpenPOWER" zur Verfügung.

Der Name PowerPC ist ein Akronym, wobei Power für Performance optimization with enhanced RISC (Leistungsoptimierung durch verbessertes RISC) und PC für Performance Chip (Leistungs-Chip) steht.

Technik und Einsatzgebiete[Bearbeiten | Quelltext bearbeiten]

PowerPC wurde von Anfang an als eine 64-Bit-Prozessorarchitektur auf RISC-Basis entworfen, wobei auch 32-Bit-Versionen verfügbar sind (bei IBM „Subset“ genannt).[1] PowerPC beherrschen Gleitkommazahlen doppelter und einfacher Genauigkeit und arbeiten im Big-Endian-Modus, manche Prozessormodelle können jedoch alternativ auf den Little-Endian-Modus umschalten. Fast alle Prozessoren neuerer Bauart verfügen auch über die von Motorola entwickelte AltiVec-Vektoreinheit oder das IBM-Äquivalent VMX. AltiVec wurde mit dem PowerPC 7400 alias PowerPC G4 eingeführt. Der letzte Vertreter der PowerPC-Familie, der noch der AIM-Allianz entstammt, ist der Doppelkern-Prozessor PowerPC 970MP sowie dessen Einkern-Version PowerPC 970GX – von Apple als PowerPC G5 vermarktet steht er gemeinsam mit dessen Vorversionen PowerPC 970 und 970FX mit bis zu 2,7 GHz Taktfrequenz für die letzten von Apple als Power Macintosh gebauten Desktop- und (als Xserve) Server-Computer.

Neuere Versionen des PowerPC-Prozessors tragen keine Generations-Bezeichnung mehr (wie G3, G4, G5).

Der Gekko (CPU im Nintendo GameCube) weist als Besonderheit spezielle Befehle auf, mit denen paarweise einfach-genaue Gleitkommazahlen, die sich in Floatingpoint-Registern befinden, bearbeitet werden können. Die Opcodes der Befehle überschneiden sich mit denen der AltiVec-Befehle.

Computer[Bearbeiten | Quelltext bearbeiten]

PowerPC-Prozessoren werden u. a. in der IBM pSeries (RS/6000) und im IBM Blade JS20 und JS21 sowie in den Motorola-PowerStack-Rechnern eingesetzt. Seit 1996 basieren auch Amiga-Rechner faktisch auf PowerPC-Prozessoren, und auch kompatible Systeme wie der Pegasos-Rechner von Genesi und der AmigaOne von Eyetech setzen ihn ein.

Apple verwendete die Prozessoren zwischen 1994 und 2006 für die Herstellung der eigenen Computer, wechselte dann jedoch zu x86-Prozessoren von Intel.[2] Allerdings kaufte Apple im April 2008 die Firma P.A. Semi auf, die eine besonders stromsparende Variante der G5-Prozessoren entwickelte. Die Zielsetzung dieses Geschäftes war zunächst unklar, später stellte sich heraus, dass Apple den so eingekauften Sachverstand für die Entwicklung eigener Prozessoren nutzte.

Eingebettete Systeme[Bearbeiten | Quelltext bearbeiten]

Auch in vielen eingebetteten Systemen kommen PowerPC-Prozessoren zum Einsatz.

Bei Heimanwendern sind dies zum Beispiel Digitalreceiver wie die d-box 2 (PPC823) oder die Dreambox (PPC405), sowie Spielekonsolen wie Nintendos GameCube, Wii und Wii U, Microsofts Xbox 360 sowie (in Form des Cells in) Sonys PlayStation 3.

Auch in PKW und in der zivilen und militärischen Luft- und Raumfahrt kommt die PowerPC-Architektur zum Einsatz. Mehrere zum Mars gesandte „Orbiter“ und „Lander“ basieren auf verschiedenen PowerPC-Varianten, zum Beispiel verwendet der Mars Reconnaissance Orbiter eine gegen Strahlung geschützte Variante des G3. Auch die Kampfflugzeuge F-22 Raptor und F-35, der AN/ALR-93 oder der AN/ALQ-135M verwenden PowerPC-CPUs, insbesondere im Bereich der Signalverarbeitung.

Geschichte und Zukunft[Bearbeiten | Quelltext bearbeiten]

Das Konsortium wurde auf Bestreben von Apple gegründet, die einen Nachfolger für die von ihnen verwendeten 680x0-Prozessoren von Motorola (ab 2004 Freescale, 2015 von NXP Semiconductors übernommen) suchten. Der von IBM für deren High-End-Workstations entwickelte POWER-Prozessor war wegen seiner leistungsfähigen und erweiterbaren Architektur ein interessanter Kandidat, jedoch in der Fertigung viel zu teuer, da es sich zum damaligen Zeitpunkt noch um ein Modul mit mehreren Chips handelte. Motorola brachte in die Entwicklung die Speicherverwaltungs- und Puffer-Einheit ihrer 88000-RISC-Prozessoren ein (die 88k-Familie wurde daraufhin eingestellt, die 68k-Familie existiert heute noch als Mikrocontroller und bildet auch die Basis für die hierzu kompatible ColdFire-Familie).

Gleichzeitig mit der Entwicklung der PowerPC-Prozessoren wurde mit der PowerPC Reference Platform, kurz PReP, auch eine Referenzplattform geschaffen, die zur Konkurrenz der etablierten, Intel-basierten PCs mit dem Betriebssystem Windows („Wintel“) werden sollte. Dabei zeigte sich dann allerdings, dass die Allianz der drei Firmen nicht in allen Belangen einer Meinung war; und die ohnehin eher zurückhaltenden Bemühungen verliefen später im Sande.

PReP wurde kurze Zeit später durch die Common Hardware Reference Platform, kurz CHRP, abgelöst, die ab 1995 in PowerPC Platform umbenannt worden war. Der jüngste, kommerziell erhältliche Spross dieser Familie war der IBM-zertifizierte Pegasos von Genesi, der auch durch Freescale vertrieben wurde.

2004 schlossen sich mehrere Firmen unter Power.org zusammen. Das Design des PowerPC 450[3] und des Pegasos wurde offengelegt[4] und die Power Architecture Platform Reference, kurz PAPR, löste CHRP (bzw. die PowerPC Platform) als Plattform-Spezifikation ab.

Am 6. Juni 2005 kündigte Apple an, die PowerPC-Architektur aufzugeben und künftig PC-Systeme mit x86-Architektur mit Prozessoren von Intel zu fertigen. (Ab 2020 begann der Übergang zur Arm-Architektur, wobei Apple die Prozessoren selbst entwickelt und bei TSMC fertigen lässt.)

In einem am 6. Dezember 2005 veröffentlichten Interview bekräftigte der CEO von Freescale, Michel Mayer, u. a. als Konsequenz hieraus die Entscheidung, die PowerPC-Baureihe ggf. umzubenennen und sich bei der weiteren Vermarktung nicht weiter um den Desktop-/Laptop-Markt zu kümmern.

Auf der Ende Juni 2005 abgehaltenen 20. Internationalen Supercomputer-Konferenz ISC 2005 zeigte sich außerdem, dass sechs der zehn zu diesem Zeitpunkt schnellsten Computer der Welt auf PowerPC basierten, davon fünf auf dem PowerPC 440 (eServer BlueGene).[5]

Der Schwerpunkt der Einsatzgebiete der PowerPC-Architektur verlagert sich somit an die beiden Enden der Skala: den Bereich eingebetteter Systeme einerseits und den Hochleistungsserverbereich andererseits.

2013 wurde mit der OpenPOWER Foundation eine Allianz zur gemeinsamen Fertigung von Power-basierten Produkten zwischen IBM, Google, Nvidia, Mellanox, Tyan[6] und Samsung[7] gegründet.

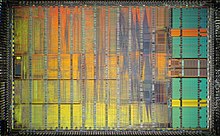

PowerPC-Generationen und -Modelle (Auswahl)[Bearbeiten | Quelltext bearbeiten]

Erste Generation G1

- MPC601 – 50, 66, 80 und 100 MHz, 32 KByte Unified L1 Cache, L2 Cache bis 1 MByte; 0,6 µm Herstellungsprozess (1993, verwendet u. a. in der ersten Power-Mac-Generation)

- MPC601+ – 110 und 120 MHz, sonst wie MPC601; 0,6 µm Herstellungsprozess

- MPC602 – speziell für Embedded-Anwendungen (gemultiplexter Daten-/Adressbus); 0,6 µm Herstellungsprozess

Zweite Generation G2

- MPC603 – 66 bis 80 MHz, 16 KByte (8 KByte Instruction, 8 KByte Data), L2 Cache bis 1 MByte; vor allem für den mobilen und „Low Cost“-Bereich; 0,5 µm Herstellungsprozess

- MPC603e – 100 bis 200 MHz, ab 166 MHz 32 KByte L1 Cache (16 KByte Instruction, 16 KByte Data), L2 Cache bis 1 MByte (größere L1 Caches für bessere 68k Emulator-Performance); 0,5 µm Herstellungsprozess

- MPC603ev – 225 bis 300 MHz, 32 KByte L1 Cache (16 KByte Instruction, 16 KByte Data), L2 Cache bis 1 MByte; 0,35 µm Herstellungsprozess

- MPC604 – 100 bis 180 MHz, 32 KByte L1 Cache (16 KByte Instruction, 16 KByte Data), L2 Cache bis 1 MByte; der 604 war vor dem 603 erhältlich (1994) und der erste High End PowerPC; 0,5 µm Herstellungsprozess

- MPC604e – 166 bis 233 MHz, 64 KByte L1 Cache (32 KByte Instruction, 32 KByte Data), L2 Cache bis 1 MByte; 0,35 µm Herstellungsprozess

- MPC604r – 250 bis 375 MHz, 64 KByte L1 Cache (32 KByte Instruction, 32 KByte Data), L2 Inline-Cache bis 1 MByte; 0,25 µm Herstellungsprozess (300- und 350-MHz-Modell) oder 0,35 µm (250-MHz-Modell), Codename „Mach 5“ und „Helmwind“

- MPC620 – 64 KByte L1 Cache (32 KByte Instruction, 32 KByte Data), 1 bis 128 MByte L2 Cache; die erste 64-Bit-PowerPC-Implementierung (nicht POWER)

- x704 BiCOMOS PowerPC Implementierung von Exponential Technologies (nie verfügbar)[8]

Dritte Generation G3

- MPC750 – 200 bis 366 MHz, 0,25 µm Herstellungsprozess, Codename „Arthur“, eingeführt 1997

- MPC750CX – 350 bis 550 MHz, 64 KByte L1 Cache (32 KByte Instruction, 32 KByte Data), 256 KByte on-Chip L2 Cache, 0,18 µm Herstellungsprozess; Codename „Sidewinder“

- MPC750CXe – 400 bis 700 MHz, 64 KByte L1 Cache (32 KByte Instruction, 32 KByte Data), 256 KByte on-Chip L2 Cache, L3 Cache extern möglich, 0,18 µm Herstellungsprozess; Codename „Anaconda“

- MPC750FX – 600 bis 1000 MHz, 64 KByte L1 Cache (32 KByte Instruction, 32 KByte Data), 512 KByte on-Chip L2 Cache, L3 Cache extern möglich, 0,13 µm Herstellungsprozess; Codename „Sahara“

- MPC750GX – 733 bis 1000 MHz, 64 KByte L1 Cache (32 KByte Instruction, 32 KByte Data), 1024 KByte on-Chip L2 Cache, L3 Cache extern möglich, 0,13 µm Herstellungsprozess; Codename „Gobi“

- Gekko 485 MHz (verwendet im Nintendo GameCube)

- RAD750 – Strahlungsresistente Version für Anwendungen in der Raumfahrt

Vierte Generation G4

- MPC7400 – 350 bis 500 MHz, 32 KByte/32 KByte Data/Instruction L1 Cache, maximal 2 MByte L2 Cache (ECC und non-ECC), Verlustleistung max. 11 Watt, erster PowerPC mit AltiVec, Codename „Max“

- MPC7410 – 400 bis 550 MHz, 32 KByte/32 KByte Data/Instruction L1 Cache, maximal 2 MByte L2 Cache (ECC und non-ECC), Verlustleistung max. 11 Watt

- MPC7441 – 600 und 700 MHz, 32 KByte/32 KByte Data/Instruction L1 Cache, 256 KByte L2 Cache on Chip, maximal 2 MByte L3 Cache; Low Power-Version des 7450/7451

- MPC7445 – 600 bis 1000 MHz, 32 KByte/32 KByte Data/Instruction L1 Cache, 256 KByte L2 Cache on Chip, Verlustleistung max. 26 Watt

- MPC7447 – 600 bis 1267 MHz, 32 KByte/32 KByte Data/Instruction L1 Cache, 256 oder 512 KByte L2 Cache on Chip, Verlustleistung max. 26 Watt, kein L3 Cache

- MPC7447A – 600 bis 1420 MHz, 32 KByte/32 KByte Data/Instruction L1 Cache, 512 KByte L2 Cache on Chip, Verlustleistung max. 29 Watt

- MPC7448 – 600 bis 2000 MHz, 32 KByte/32 KByte Data/Instruction L1 Cache, 1024 KByte L2 Cache mit ECC on Chip, Verlustleistung ca. 10 Watt bei 1,5 GHz

- MPC7450 – 533 bis 867 MHz, 32 KByte/32 KByte Data/Instruction L1 Cache, Codename „Voyager“

- MPC745 – 300 bis 350 MHz, 32 KByte/32 KByte Data/Instruction L1 Cache, Verlustleistung max. 5,3 Watt

- MPC7451 – 533 bis 867 MHz, 32 KByte/32 KByte Data/Instruction L1 Cache, 256 KByte L2 Cache on Chip, maximal 2 MByte L3 Cache

- MPC7455 – 600 bis 1425 MHz, 32 KByte/32 KByte Data/Instruction L1 Cache, 256 KByte L2 Cache on Chip, maximal 2 MByte L3 Cache, Verlustleistung max. 45 Watt, Codename „Apollo“

- MPC7457 – 600 bis 1333 MHz, 32 KByte/32 KByte Data/Instruction L1 Cache, 512 KByte L2 Cache on Chip, maximal 2 MByte L3 Cache, Verlustleistung max. 25 Watt

- MPC755 – 300 bis 400 MHz, 32 KByte/32 KByte Data/Instruction L1 Cache, maximal 1 MByte L3 Cache, Verlustleistung max. 8 Watt

Fünfte Generation G5

- 970 – 64-Bit-Implementierung, abgeleitet vom IBM POWER4, erweitert um VMX (IBMs Äquivalent zu Motorolas AltiVec) mit 1,4 GHz, 1,6 GHz, 1,8 GHz, und 2,0 GHz Taktfrequenz (2003)

- 970FX – mit bis zu 2,5 GHz Taktfrequenz (2004), von Apple auf 2,7 GHz übertaktet

- 970MP – Dual Core mit 1,4 bis 2,5 GHz Takt (2005); Codename „Antares“

- 970GX – bis zu 3 GHz Takt. Bei 1,6 GHz 16 W Leistungsaufnahme, 85 W bei 3 GHz (2006)

Betriebssysteme[Bearbeiten | Quelltext bearbeiten]

Die meisten aktuellen Versionen der gelisteten Betriebssysteme haben heute (Stand: 2017) keine (offizielle) Unterstützung für die PowerPC-Architektur mehr, da der PowerPC-Prozessor auch nicht mehr in aktuellen Desktop-Systemen, Workstations und Servern zu finden ist. Es gibt jedoch Versionen für Embedded-Systeme und inoffizielle Ports für ältere PowerPC-Desktop-Computer (wie etwa die Apple Power-Macintosh-Reihe).

- IBM AIX

- AmigaOS (Version 4)

- AROS

- BeOS

- Darwin (bis Version 9), auch als „Darwin OS“ und „OpenDarwin“

- FreeBSD

- HelenOS

- IBM i for Business (vormals OS/400)

- INTEGRITY Echtzeitbetriebssystem von Green Hills

- Linux (z. B. LinuxPPC – gängige Linux-Distributionen: Ubuntu bis Version 6.10, Debian bis Version 8 „Jessie“, Lubuntu 16.04.3 LTS)

- Apple Mac OS ab System 7.1.2 und Mac OS X bis 10.5.8 „Leopard“

- MorphOS

- MQX

- MUNIX

- NetBSD

- OpenBSD

- IBM OS/2 Warp Power Edition

- OS-9

- PikeOS

- Plan 9

- PowerUP/WarpUP PowerPC Kernel (für AmigaOS bis Version 3.9)

- QNX

- SCIOPTA[9] Zertifiziert nach IEC 61508, EN 50128 und ISO 26262.

- Sun Solaris (Release 2.5.1) bzw. „Polaris“

- VxWorks

- Microsoft Windows NT, Versionen 3.51 und 4.0

Weblinks[Bearbeiten | Quelltext bearbeiten]

- realworldtech – PowerPC 970GX Vorstellung auf der SSCC 2006 in San Francisco.

- Cnet Interview mit Freescale CEO Michel Mayer über die Zukunft des PowerPC

- PowerPC Prozessoren: Bilder und Beschreibungen (englisch)

- Eine Community rund um die POWER-Architektur (englisch)

- Polaris (englisch)

- FreeBSD/ppc Project (englisch)

- Macinfo – Prozessoren-Übersicht (nicht nur PowerPC)

- Christian Persson, Andreas Stiller, Carsten Meyer, Peter Siering: Showdown bei Zwo-Null-Null – Nur die Leistung zählt: PowerPC gegen Pentium und Pentium Pro. In: Heise online. 12. Oktober 1996. Abgerufen am 9. März 2016.

Einzelnachweise[Bearbeiten | Quelltext bearbeiten]

- ↑ Daniel Tabak: RISC Systems and Applications. Research Studies Press, University of California 1996, ISBN 978-0-471-96027-0, S. 148 (englisch, 435 S., eingeschränkte Vorschau in der Google-Buchsuche ): “It should be noted that the PowerPC architecture was designed from the beginning with future 64-bit implementations in mind. The PowerPC architecture was defined as a 64-bit architecture with a 32-bit subset.”

- ↑ Stephan Ehrmann: WWDC: Apple steigt um auf Intel-Architektur. In: Heise online. 6. Juni 2005 (4. Update). Abgerufen am 9. März 2016.

- ↑ Mattias Hermannstorfer: Forscher erhalten Einblick in PowerPC-Spezifikationen. In: Heise online. 15. Dezember 2005. Abgerufen am 13. Februar 2022.

- ↑ Mattias Hermannstorfer: Design des PowerPC-Mainboards Pegasos veröffentlicht. In: Heise online. 12. Januar 2006. Abgerufen am 13. Februar 2022.; Zitat: „Die vollständige Designunterlagen für das PowerPC-basierte Mainboard Pegasos lassen sich nun von der Webseite der PowerPC-Community Power.org herunterladen.“.

- ↑ Andreas Stiller: Top500 der Supercomputer: IBM dominiert. In: Heise online. 22. Juni 2005 (Bericht über die 20. internationale Supercomputer-Konferenz „ISC 2005“ in Heidelberg). Abgerufen am 9. März 2016.

- ↑ Christof Windeck: IBM sucht neue Kunden für Power-Prozessoren. In: Heise online. 6. August 2013. Abgerufen am 13. Februar 2022.

- ↑ Christof Windeck: Samsung tritt der OpenPOWER-Foundation bei. In: Heise online. 13. Februar 2014. Abgerufen am 13. Februar 2022.

- ↑ Carsten Meyer: Exponential zeigt X704-Mac mit 450 MHz. In: Heise online. 15. März 1997. Abgerufen am 9. März 2016.

- ↑ http://www.sciopta.com SCIOPTA; RTOS.